Description

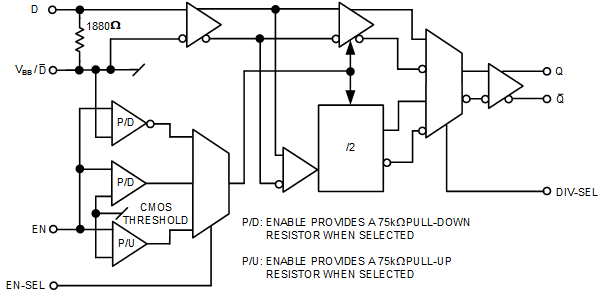

The AZP92 is a ÷1 or ÷2 clock generation part specifically designed to accommodate Colpitts or Pierce based oscillators. Features are incorporated to reduce board components. A voltage reference and input biasing allows for easy oscillator interface.

The AZP92 provides a ÷ 2 mode of operation for more frequency options and is selectable with a single connection. A selectable enable is also provided which doubles as a reset when the AZP92 is in ÷2 mode. With a single connection, the enable can be selected to operate as active high or active low.

EOL – Not recommended for new designs

Block Diagram

- • Selectable divide ratio

- • Selectable enable polarity & threshold

- • Up to 3.0GHz operation

- •3.3V – 5V analog supply

- • Pierce or Colpitts Oscillators

- • Crystal or SAW Oscillators

Order Numbers

| Part Number | Package | Dimensions | Quantity | MSL Rating |

|---|---|---|---|---|

| AZP92NAG | MLP8 | 2mm x 2mm | 1000 | 1 |