Description

The AZP63 is a sine wave/CMOS to LVPECL translator / buffer optimized for very low phase noise and additive jitter operating at 3.3V & 5.0V nominal supply voltages. It is particularly useful in converting crystal or SAW based oscillators into LVPECL outputs for up 1.2 GHz of bandwidth. The AZP63 is a high frequency variant of a family of parts that provide options of fixed ÷1, fixed ÷2 and selectable ÷1, ÷2 modes as well as active high enable or active low enable to oscillator designers.

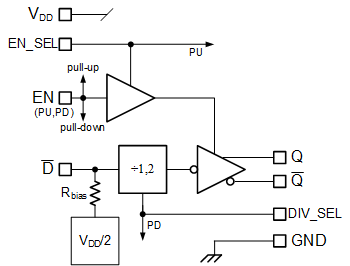

Block Diagram

- • 50fs additive jitter

- • -165dBc/Hz phase noise floor

- • Up to 1.2 GHz operation

- • Internal divider

- • 3.3V – 5.0V analog supply

- • Industrial Temp Range: -40°C to 85°C

- • Crystal or SAW Oscillators

- • Clock references and drivers

- • Signal conversion

- • Clock fanout

Order Numbers

| Part Number | Package | Dimensions | Quantity | MSL Rating | Leadframe |

|---|---|---|---|---|---|

| AZP63QGR1 | SON8 | 1.5mm x 1.0mm | 1000 | 1 | NiPdAu |